3-8 译码器的设计

用三个 bit 的输入信号来得到八个 bit 的输出信号,一个十分自然的思路便是使用二进制编码:毕竟我们有 $2^3=8$ 。如果我们将作为输入信号的三个 bit 记作 $I_0, I_1, I_2$, 作为八个输出信号的 bit 记作 $O_0, O_1, \dots, O_8$ ,那么我们可以作出如下的真值表:

| Index | $I_2$ | $I_1$ | $I_0$ | $O_0$ | $O_1$ | $O_2$ | $O_3$ | $O_4$ | $O_5$ | $O_6$ | $O_7$ |

|---|---|---|---|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| 2 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| 3 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| 4 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 5 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 6 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 7 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

很显然,如果我们将 $O_0, \dots, O_7$ 作为八个布尔函数来看的话,它们都只有唯一一个值为1的最小项,所以这个最小项便是它们的最简表达式。因此我们有

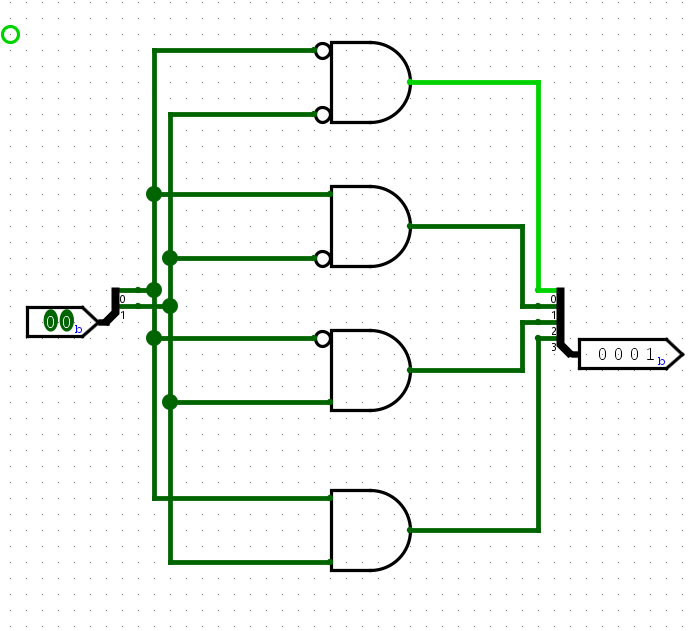

通过 Logisim-Evolution 与布尔函数画出电路图并模拟运行如下:

由图可知,电路符合我们的要求。

使用 2-4 译码器实现 3-8 译码器

这是一个 2-4 译码器的电路结构

现在我们需要用两个 2-4 译码器来实现一个 3-8 译码器。既然作为输入信号的八个三位二次元组合 $000,001,\dots,111$ 对应着八个仅一个对应的输出端为高电位的结果,我们可以将这八位输出端分割为高四位与低四位,分别由两个 2-4 译码器来控制。

但是因为在我们这里,译码器的输出会且仅仅出现一个 $1$ ,而两个译码器的输出拼接会产生两个 $1$ 出来 (例如 $0010\ 0100$),这样的结果不符合我们对译码器输出的要求,因此我们需要给两个译码器分别安装一个使能端,在同一时间内,只能有一个使能端开启,即同一时间内只能有一个译码器为激活状态,而未激活的译码器结果应输出 $0000$.

假设高四位译码器的使能端接收信号记作 $E_H$,输出的四位信号记作 $O_H$,输出结果对应的二位输入为 $I’_H$, 低四位的使能端记作 $E_L$,输出记作 $O_L$ ,输出结果对应的二位输入为 $I’_L$,三位输入记作 $I_0,I_1,I_2$,则相应的真值表如下:

| Index | $I_2$ | $I_1$ | $I_0$ | $E_H$ | $E_L$ | $O_H$ | $O_L$ | $I’_H$ | $I’_L$ |

|---|---|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 1 | 0000 | 0001 | X | 00 |

| 1 | 0 | 0 | 1 | 0 | 1 | 0000 | 0010 | X | 01 |

| 2 | 0 | 1 | 0 | 0 | 1 | 0000 | 0100 | X | 10 |

| 3 | 0 | 1 | 1 | 0 | 1 | 0000 | 1000 | X | 11 |

| 4 | 1 | 0 | 0 | 1 | 0 | 0001 | 0000 | 00 | X |

| 5 | 1 | 0 | 1 | 1 | 0 | 0010 | 0000 | 01 | X |

| 6 | 1 | 1 | 0 | 1 | 0 | 0100 | 0000 | 10 | X |

| 7 | 1 | 1 | 1 | 1 | 0 | 1000 | 0000 | 11 | X |

观察真值表,我们可以得到一些重要性质,这对我们设计电路有巨大作用:

- 当 $I_2$ 为低电位, $E_H$ 关闭, $E_L$ 开启,当 $I_2$ 为高电位, $E_H$ 开启, $E_L$ 关闭

- $I’_H$ 与 $I’_L$ (如果使能端未关闭) 的组合始终与 $I_1I_0$ 的组合相同

综上,我们可以直接将 $I_0$ 与 $I_1$ 都同时接入两个译码器,同时引入 $I_2$ 作为使能端,一个取反值接入低四位译码器,另一个取原值接入高四位译码器。电路图如下:

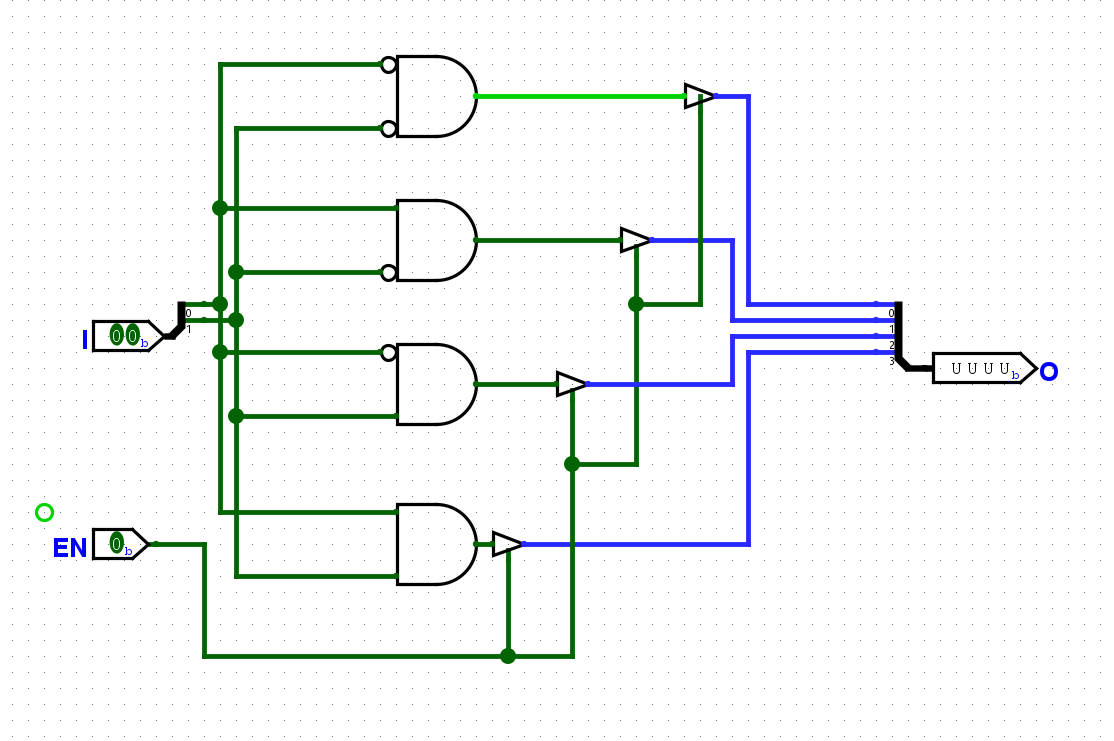

首先是安装使能端的 2-4 译码器

以及由其构造的 3-8 译码器

借助 3-8 译码器进行楼道灯控制

楼道灯控制是指:在一个楼道中,有三个开关控制一盏灯是否亮,且改变其中任意一个开关的状态时,灯的状态都会随之改变。

例如,若某一时刻时,三个开关的状态分别是闭合、断开、闭合,而此时灯灭,则此时,将任意一个闭合的开关断开,或者将任意一个断开的开关闭合,则灯亮(即三个开关均闭合,或三个开关的状态分别为闭合、断开、断开,或三个开关的状态分别为断开、断开、闭合时,灯均亮)

听起来有点像异或:每当有一位输入的信号改变,最后输出的1位信号都要改变。但是我们这里需要使用 3-8 译码器,一个直观的思路就是通过译码器的 8 位输出来控制灯的开关。注意到改变其中任意一个开关的状态,相当于将输入的二次元组合转为另一个相邻的二次元组合,这让我们想到格雷码,进而发现,假如我们将灯的开关状态作为一个关于 $I_0,I_1,I_2$ 的布尔函数,可以做出一个卡诺图:

| $I_0$ / $I_1,I_2$ | 00 | 01 | 11 | 10 |

|---|---|---|---|---|

| 0 | $1_0$ | $0_1$ | $1_3$ | $0_2$ |

| 1 | $0_4$ | $1_5$ | $0_7$ | $1_6$ |

因此,我们可以将 $O_0, O_3, O_5, O_6$ 接入一个或门,用于控制灯的开关,另外四个信号作为无用信号排除。

得到的电路图如下: